# **DSP Microcomputer**

# **ADSP-2192M**

ADSP-2192M DUAL CORE DSP FEATURES

320 MIPS ADSP-219x DSP in a 144-Lead LQFP Package with PCI, USB, Sub-ISA, and CardBus Interfaces

3.3 V/5.0 V PCI 2.2 Compliant 33 MHz/32-bit Interface with Bus Mastering over Four DMA Channels with Scatter-Gather Support

Integrated USB 1.1 Compliant Interface Sub-ISA Interface

AC'97 Revision 2.1 Compliant Interface for External Audio, Modem, and Handset Codecs with DMA Capability

Dual ADSP-219x Core Processors (P0 and P1) on Each ADSP-2192M DSP Chip

132K Words of Memory Includes 4K × 16-Bit Shared Data Memory

80K Words of On-Chip RAM on P0, Configured as 64K Words On-Chip 16-Bit RAM for Data Memory and 16K Words On-Chip 24-Bit RAM for Program Memory

48K Words of On-Chip RAM on P1, Configured as 32K Words On-Chip 16-Bit RAM for Data Memory and 16K Words On-Chip 24-Bit RAM for Program Memory

4K Words of Additional On-Chip RAM Shared by Both Cores, Configured as 4K Words On-Chip 16-Bit RAM

Flexible Power Management with Selectable Power-Down and Idle Modes

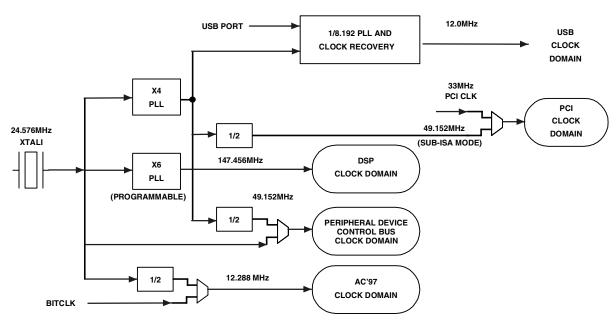

Programmable PLL Supports Frequency Multiplication, Enabling Full Speed Operation from Low Speed Input Clocks

2.5 V Internal Operation Supports 3.3 V/5.0 V Compliant I/O

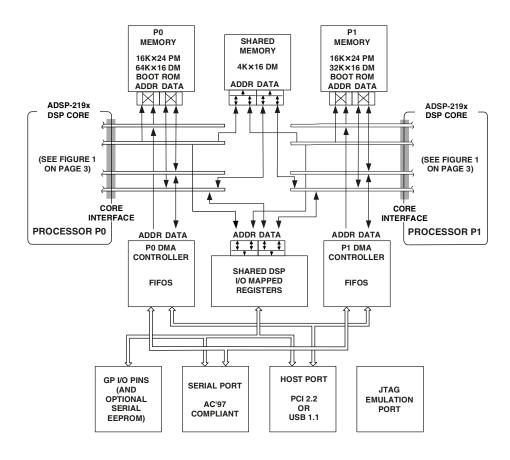

#### FUNCTIONAL BLOCK DIAGRAM

#### REV. 0

| ADSP-2192M DUAL CORE DSP FEATURES (continued) Eight Dedicated General-Purpose I/O Pins with Integrated Interrupt Support | TABLE OF CONTENTS GENERAL DESCRIPTION |

|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Each DSP Core Has a Programmable 32-Bit Interval Timer                                                                   | DSP Peripherals                       |

| Five DMA Channels Available on Each Core                                                                                 | Memory Architecture 4                 |

| Boot Methods Include Booting Through PCI Port, USB                                                                       | Interrupts                            |

| Port, or Serial EEPROM                                                                                                   | DMA Controller 6                      |

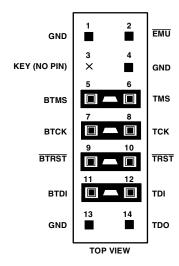

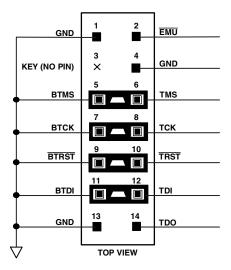

| JTAG Test Access Port Supports On-Chip Emulation and                                                                     | External Interfaces 6                 |

| System Debugging                                                                                                         | Internal Interfaces                   |

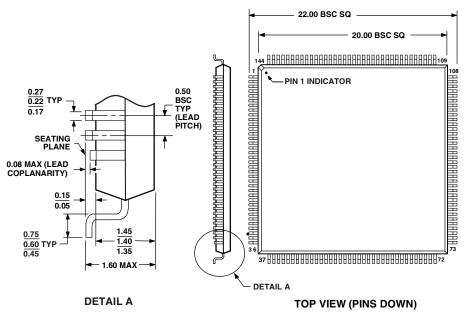

| 144-Lead LQFP Package                                                                                                    | Register Spaces                       |

|                                                                                                                          | CardBus Interface                     |

| DSP CORE FEATURES                                                                                                        | Using the PCI Interface               |

| 6.25 ns Instruction Cycle Time (Internal), for up to                                                                     | Using the USB Interface               |

| 160 MIPS Sustained Performance                                                                                           | General USB Device Definitions        |

| ADSP-218x Family Code Compatible with the Same Easy                                                                      | Sub-ISA Interface                     |

| to Use Algebraic Syntax                                                                                                  | PCI Interface to DSP Memory           |

| Single-Cycle Instruction Execution                                                                                       | USB Interface to DSP Memory           |

| Dual Purpose Program Memory for Both Instruction and                                                                     | AC'97 Codec Interface to DSP Memory   |

| Data Storage Fully Transparent Instruction Cache Allows Dual Operand                                                     | Data FIFO Architecture                |

| Fetches in Every Instruction Cycle                                                                                       | System Reset Description              |

| Unified Memory Space Permits Flexible Address                                                                            | Power Management Description          |

| Generation, Using Two Independent DAG Units                                                                              | Power Regulators                      |

| Independent ALU, Multiplier/Accumulator, and Barrel                                                                      | 2.5 V Regulator Options               |

| Shifter Computational Units with Dual 40-Bit                                                                             | Low Power Operation                   |

| Accumulators                                                                                                             | Clock Signals                         |

| Single-Cycle Context Switch between Two Sets of                                                                          | Instruction Set Description           |

| Computational and DAG Registers                                                                                          | Development Tools                     |

| Parallel Execution of Computation and Memory                                                                             | Additional Information                |

| Instructions                                                                                                             | PIN DESCRIPTIONS                      |

| Pipelined Architecture Supports Efficient Code Execution                                                                 | SPECIFICATIONS                        |

| at Speeds up to 160 MIPS                                                                                                 | ABSOLUTE MAXIMUM RATINGS              |

| Register File Computations with All Nonconditional,                                                                      | ESD SENSITIVITY                       |

| Nonparallel Computational Instructions                                                                                   | TIMING SPECIFICATIONS                 |

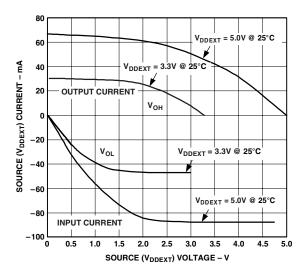

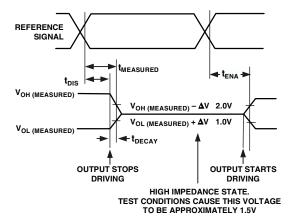

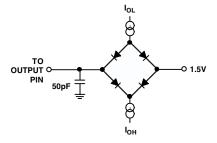

| Powerful Program Sequencer Provides Zero-Overhead                                                                        | Output Drive Currents                 |

| Looping and Conditional Instruction Execution                                                                            | Power Dissipation                     |

| Architectural Enhancements for Compiled C/C++ Code                                                                       | Test Conditions                       |

| Efficiency                                                                                                               | Environmental Conditions              |

| Architecture Enhancements beyond ADSP-218x Family are Supported with Instruction Set Extensions for                      | 144-Lead LQFP Pinout                  |

| Added Registers, Ports, and Peripherals                                                                                  | OUTLINE DIMENSIONS                    |

| Auded hegisters, Forts, and Felipherals                                                                                  | ORDERING GUIDE                        |

|                                                                                                                          |                                       |

-2- REV. 0

#### **GENERAL DESCRIPTION**

The ADSP-2192M is a single-chip microcomputer optimized for digital signal processing (DSP) and other high speed numeric processing applications, and is ideally suited for PC peripherals.

The ADSP-2192M combines the ADSP-219x family base architecture (three computational units, two data address generators and a program sequencer) into a chip with two core processors (see the Functional Block Diagram on Page 1 and Figure 1).

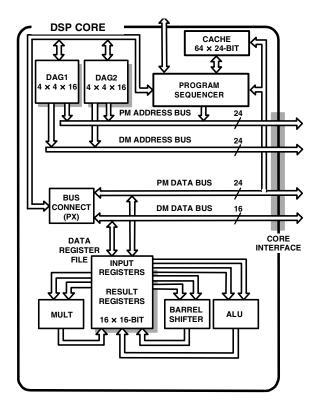

Figure 1. ADSP-219x DSP Core

The ADSP-2192M includes a PCI-compatible port, a USB-compatible port, an AC'97-compatible port, a DMA controller, a programmable timer, general-purpose Programmable Flag pins, extensive interrupt capabilities, and on-chip program and data memory spaces.

The ADSP-2192M integrates 132K words of on-chip memory configured as 32K words (24-bit) of program RAM, and 100K words (16-bit) of data RAM. power-down circuitry is also provided to reduce power consumption. The ADSP-2192M is available in a 144-lead LQFP package.

Fabricated in a high speed, low power, CMOS process, the ADSP-2192M operates with a 6.25 ns instruction cycle time (320 MIPS) using both cores. All instructions can execute in a single DSP cycle.

The ADSP-2192M's flexible architecture and comprehensive instruction set support multiple operations in parallel. For example, in one processor cycle, each DSP core within the ADSP-2192M can:

- Generate an address for the next instruction fetch

- Fetch the next instruction

- Perform one or two data moves

- Update one or two data address pointers

- Perform a computational operation

These operations take place while the processor continues to:

- Receive and/or transmit data through the Host port (PCI or USB interfaces)

- Receive or transmit data through the AC'97

- Decrement the two timers

#### **DSP** Core Architecture

The ADSP-219x architecture is code compatible with the ADSP-218x DSP family. Though the architectures are compatible, the ADSP-219x architecture has many enhancements over the ADSP-218x architecture. The enhancements to computational units, data address generators, and program sequencer make the ADSP-219x more flexible and more compiler friendly.

Indirect addressing options provide addressing flexibility: base address registers for easier implementation of circular buffering, pre-modify with no update, post-modify with update, pre- and post-modify by an immediate 8-bit, twos-complement value.

The ADSP-219x instruction set provides flexible data moves and multifunction (one or two data moves with a computation) instructions. Every single-word instruction can be executed in a single processor cycle. The ADSP-219x assembly language uses an algebraic syntax for ease of coding and readability. A comprehensive set of development tools supports program development.

The Functional Block Diagram on Page 1 shows the architecture of the ADSP-219x dual core DSP, while the block diagram of Figure 1 illustrates the ADSP-219x DSP core. Each core contains three independent computational units: the multiplier/accumulator (MAC), the ALU, and the shifter. The computational units process 16-bit data from the register file and have provisions to support multiprecision computations. The ALU performs a standard set of arithmetic and logic operations; division primitives are also supported. The MAC performs single-cycle multiply, multiply/add, and multiply/subtract operations. The MAC has two 40-bit accumulators that help with overflow. The shifter performs logical and arithmetic shifts, normalization, denormalization, and derive exponent operations. The shifter can be used to efficiently implement numeric format control, including multiword and block floating-point representations.

Register-usage rules influence placement of input and results within the computational units. For most operations, the computational units' data registers act as a data register file, permitting any input or result register to provide input to any unit for a computation. For feedback operations, the computational units let the output (result) of any unit be input to any unit on

the next cycle. For conditional or multifunction instructions, there are restrictions on which data registers may provide inputs or receive results from each computational unit. For more information, see the ADSP-219x DSP Instruction Set Reference.

A powerful program sequencer controls the flow of instruction execution. The sequencer supports conditional jumps, subroutine calls, and low interrupt overhead. With internal loop counters and loop stacks, the ADSP-219x core executes looped code with zero overhead; no explicit jump instructions are required to maintain loops.

Two data address generators (DAGs) provide addresses for simultaneous dual operand fetches. Each DAG maintains and updates four 16-bit address pointers. Whenever the pointer is used to access data (indirect addressing), it is pre- or post-modified by the value of one of four possible modify registers. A length value and base address may be associated with each pointer to implement automatic modulo addressing for circular buffers. Page registers in the DAGs allow linear or circular addressing within 64K word boundaries of each of the memory pages, but these buffers may not cross page boundaries. Secondary registers duplicate all the primary registers in the DAGs; switching between primary and secondary registers provides a fast context switch.

Efficient data transfer in the core is achieved with the use of internal buses:

- Program Memory Address (PMA) Bus

- Program Memory Data (PMD) Bus

- Data Memory Address (DMA) Bus

- Data Memory Data (DMD) Bus

Program memory can store both instructions and data, permitting the ADSP-219x to fetch two operands in a single cycle, one from program memory and one from data memory. The DSP's dual memory buses also let the ADSP-219x core fetch an operand from data memory and the next instruction from program memory in a single cycle.

#### **DSP** Peripherals

The Functional Block Diagram on Page 1 shows the DSP's on-chip peripherals, which include the Host port (PCI or USB), AC'97 port, JTAG test and emulation port, flags, and interrupt controller.

The ADSP-2192M can respond to up to thirteen interrupts at any given time. A list of these interrupts appears in Table 2.

The AC'97 Codec port on the ADSP-2192M provides a complete synchronous, full-duplex serial interface. This interface supports the AC'97 standard.

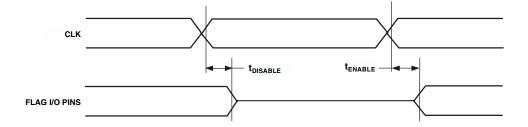

The ADSP-2192M provides up to eight general-purpose I/O pins that are programmable as either inputs or outputs. These pins are dedicated general-purpose Programmable Flag pins.

The programmable interval timer generates periodic interrupts. A 16-bit count register (TCOUNT) is decremented every n cycles where n-1 is a scaling value stored in a 16-bit register (TSCALE). When the value of the count register reaches zero, an interrupt is generated and the count register is reloaded from a 16-bit period register (TPERIOD).

#### **Memory Architecture**

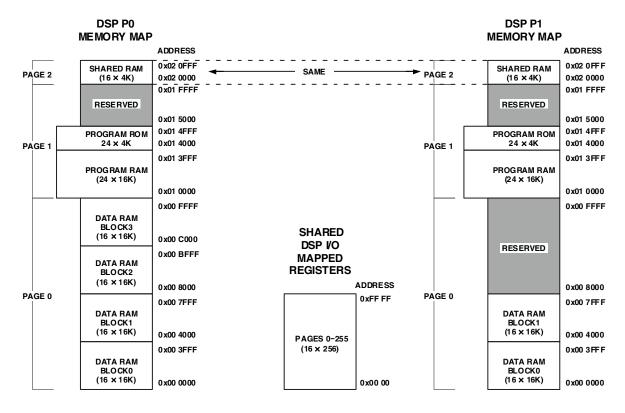

The ADSP-2192M provides 132K words of on-chip SRAM memory. This memory is divided into Program and Data Memory blocks in each DSP's memory map. In addition to the internal memory space, the two cores can address two additional and separate off-core memory spaces: I/O space and shared memory space, as shown in Figure 2.

The ADSP-2192M's two cores can access 80K and 48K locations that are accessible through two 24-bit address buses, the PMA and DMA buses. The DSP has three functions that support access to the full memory map.

- The DAGs generate 24-bit addresses for data fetches from the entire DSP memory address range. Because DAG index (address) registers are 16 bits wide and hold the lower 16 bits of the address, each of the DAGs has its own 8-bit page register (DMPGx) to hold the most significant eight address bits. Before a DAG generates an address, the program must set the DAG's DMPGx register to the appropriate memory page.

- The Program Sequencer generates the addresses for instruction fetches. For relative addressing instructions, the program sequencer bases addresses for relative jumps, calls, and loops on the 24-bit Program Counter (PC). In direct addressing instructions (two-word instructions), the instruction provides an immediate 24-bit address value. The PC allows linear addressing of the full 24-bit address range.

- For indirect jumps and calls that use a 16-bit DAG address register for part of the branch address, the Program Sequencer relies on an 8-bit Indirect Jump page (IJPG) register to supply the most significant eight address bits. Before a cross page jump or call, the program must set the program sequencer's IJPG register to the appropriate memory page.

Each ADSP-219x DSP core has an on-chip ROM that holds boot routines (See Booting Modes on Page 23.).

#### Interrupts

The interrupt controller lets the DSP respond to 13 interrupts with minimum overhead. The controller implements an interrupt priority scheme as shown in Table 2. Applications can use the unassigned slots for software and peripheral interrupts. The DSP's Interrupt Control (ICNTL) register (shown in Table 3) provides controls for global interrupt enable, stack interrupt configuration, and interrupt nesting.

-4- REV. 0

Figure 2. ADSP-2192M Internal/External Memory, Boot Memory, and I/O Memory Maps

Table 2 shows the interrupt vector and DSP-to-DSP semaphores at reset of each of the peripheral interrupts. The peripheral interrupt's position in the IMASK and IRPTL register and its vector address depend on its priority level, as shown in Table 2.

Table 1. DSP-to-DSP Semaphores Register Table

| Flag |           |                                  |

|------|-----------|----------------------------------|

| Bit  | Direction | Function                         |

| 0    | Output    | DSP-DSP Semaphore 0              |

| 1    | Output    | DSP–DSP Semaphore 1              |

| 2    | Output    | DSP-DSP Interrupt                |

| 3    |           | Reserved                         |

| 4    |           | Reserved                         |

| 5    |           | Reserved                         |

| 6    |           | Reserved                         |

| 7    | Output    | Register Bus Lock                |

| 8    | Input     | DSP-DSP Semaphore 0              |

| 9    | Input     | DSP–DSP Semaphore 1              |

| 10   | Input     | DSP-DSP Interrupt                |

| 11   | Input     | Reserved                         |

| 12   | Input     | AC'97 Register-PDC Bus Access    |

|      |           | Status                           |

| 13   | Input     | PDC Interface Busy Status (write |

|      |           | from DSP pending)                |

| 14   | Input     | Reserved                         |

| 15   | Input     | Register Bus Lock Status         |

Table 2. Vector Table

| Bit | Priority | Interrupt                      | Vector<br>Address<br>Offset <sup>1</sup> |

|-----|----------|--------------------------------|------------------------------------------|

| 0   | 1        | Reset (non-maskable)           | 0x00                                     |

| 1   | 2        | Power-Down (non-maskable)      | 0x04                                     |

| 2   | 3        | Kernel interrupt (single step) | 0x08                                     |

| 3   | 4        | Stack Status                   | 0x0C                                     |

| 4   | 5        | Mailbox                        | 0x10                                     |

| 5   | 6        | Timer                          | 0x14                                     |

| 6   | 7        | GPIO                           | 0x18                                     |

| 7   | 8        | PCI Bus Master                 | 0x1C                                     |

| 8   | 9        | DSP-DSP                        | 0x20                                     |

| 9   | 10       | FIFO0 Transmit                 | 0x24                                     |

| 10  | 11       | FIFO0 Receive                  | 0x28                                     |

| 11  | 12       | FIFO1 Transmit                 | 0x2C                                     |

| 12  | 13       | FIFO1 Receive                  | 0x30                                     |

| 13  | 14       | Reserved                       | 0x34                                     |

| 14  | 15       | Reserved                       | 0x38                                     |

| 15  | 16       | AC'97 Frame                    | 0x3C                                     |

<sup>&</sup>lt;sup>1</sup>The interrupt vector address values are represented as offsets from address 0x01 0000. This address corresponds to the start of Program Memory in DSP P0 and P1.

REV. 0 –5–

Interrupt routines can either be nested with higher priority interrupts taking precedence or processed sequentially. Interrupts can be masked or unmasked with the IMASK register. Individual interrupt requests are logically ANDed with the bits in IMASK; the highest priority unmasked interrupt is then selected. The emulation, power-down, and reset interrupts are nonmaskable with the IMASK register, but software can use the DIS INT instruction to mask the power-down interrupt.

Table 3. Interrupt Control (ICNTL) Register Bits

| Bit   | Description                 |

|-------|-----------------------------|

| 0-3   | Reserved                    |

| 4     | Interrupt nesting enable    |

| 5     | Global interrupt enable     |

| 6     | Reserved                    |

| 7     | MAC biased rounding enable  |

| 8-9   | Reserved                    |

| 10    | PC stack interrupt enable   |

| 11    | Loop stack interrupt enable |

| 12    | Low power idle enable       |

| 13-15 | Reserved                    |

The IRPTL register is used to force and clear interrupts. On-chip stacks preserve the processor status and are automatically maintained during interrupt handling. To support interrupt, loop, and subroutine nesting, the PC stack is 33 levels deep, the loop stack is eight levels deep, and the status stack is 16 levels deep. To prevent stack overflow, the PC stack can generate a stack level interrupt if the PC stack falls below three locations full or rises above 28 locations full.

The following instructions globally enable or disable interrupt servicing, regardless of the state of IMASK.

ENA INT; DIS INT;

At reset, interrupt servicing is disabled.

For quick servicing of interrupts, a secondary set of DAG and computational registers exist. Switching between the primary and secondary registers lets programs quickly service interrupts, while preserving the DSP's state.

#### **DMA Controller**

The ADSP-2192M has a DMA controller that supports automated data transfers with minimal overhead for the DSP core. Cycle stealing DMA transfers can occur between the ADSP-2192M's internal memory and any of its DMA-capable peripherals. DMA transfers can also be accomplished between any of the DMA-capable peripherals. DMA-capable peripherals include the PCI and AC'97 ports. Each individual DMA-capable peripheral has a dedicated DMA channel. DMA sequences do not contend for bus access with the DSP core; instead, DMAs "steal" cycles to access memory. All DMA transfers use the Program Memory (PMA/PMD) buses shown in the Functional Block Diagram on Page 1.

#### **External Interfaces**

Several different interfaces are supported on the ADSP-2192M. These include both internal and external interfaces. The three separate PCI configuration spaces are programmable to set up the device in various Plug-and-Play configurations.

The ADSP-2192M provides the following types of external interfaces: PCI, USB, Sub-ISA, CardBus, AC'97, and serial EEPROM. The following sections discuss those interfaces.

#### PCI 2.2 Host Interface

The ADSP-2192M includes a 33 MHz, 32-bit bus master PCI interface that is compliant with revision 2.2 of the PCI specification. This interface supports the high data rates.

#### USB 1.1 Host Interface

The ADSP-2192M USB interface enables the host system to configure and attach a single device with multiple interfaces and various endpoint configurations. The advantages of this design include:

- Programmable descriptors and class-specific command interpreter.

- An on-chip 8052-compatible MCU allows the user to soft download different configurations and support standard or class-specific commands.

- Total of eight user-defined endpoints provided.

Endpoints can be configured as either BULK, ISO, or INT, and the endpoints can be grouped and assigned to any interface.

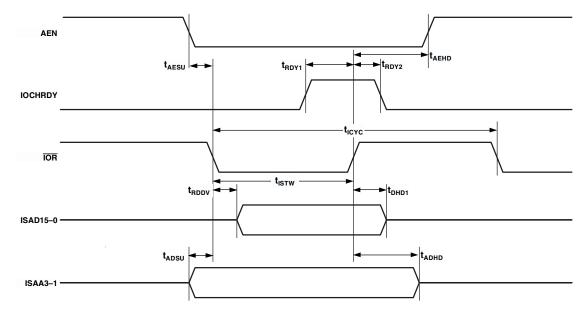

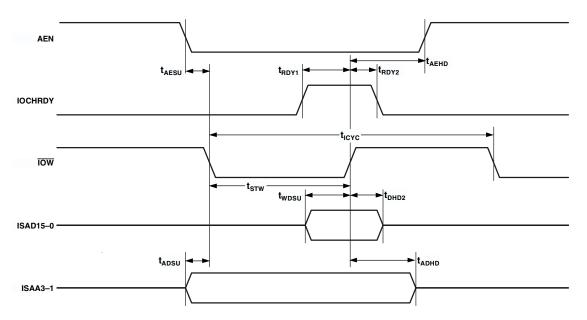

#### Sub-ISA Interface

In systems that combine the ADSP-2192M chip with other devices on a single PCI interface, the ADSP-2192M Sub-ISA mode is used to provide a simpler interface that bypasses the ADSP-2192M's PCI interface. In this mode the Combo Master assumes all responsibility for interfacing the function to the PCI bus, including provision of Configuration Space registers for the ADSP-2192M system as a separate PnP function. In Sub-ISA Mode the PCI Pins are reconfigured for ISA operation.

#### CardBus Interface

The CardBus standard provides higher levels of performance than the 16-bit PC Card standard. For example, 32-bit CardBus cards are able to take advantage of internal bus speeds that can be as much as four to six times faster than 16-bit PC Cards. This design provides for a compact, rugged card that can be completely inserted within its host computer without any external cabling.

Because CardBus performance attains the same high level as the host platform's internal (PCI) system bus, it is an excellent way to add high speed communications to the notebook form factor. In addition, CardBus PC Cards operate at a power-saving 3.3 volts, extending battery life in most configurations.

This new 32-bit CardBus technology provides up to 132M bytes per second of bandwidth. This performance makes CardBus an ideal vehicle to meet the demands of high throughput communications such as ADSL.

-6- REV. 0

CardBus PC Cards generate less heat and consume less power. This is attained by:

- Low voltage operation at 3.3 V

- Software control of clock speed

- Advanced power management mechanism

#### AC'97 2.1 External Codec Interface

The industry standard AC'97 serial interface (AC-Link) incorporates a 7-pin digital serial interface that links compliant codecs to the ADSP-2192M. The ACLink implements a bidirectional, fixed rate, serial PCM digital stream. It handles multiple input and output audio streams as well as control and status register accesses using a time division multiplex scheme.

#### Serial EEPROM Interface

The Serial EEPROM for the ADSP-2192M can overwrite the following information which is returned during the USB GET DEVICE DESCRIPTOR command. During the Serial EEPROM initialization procedure, the DSP is responsible for writing the USB Descriptor Vendor ID, USB Descriptor Product ID, USB Descriptor Release Number, and USB Descriptor Device Attributes registers to change the default settings.

All descriptors can be changed when downloading the RAM-based MCU renumeration code, except for the Manufacturer and Product, which are supported in the CONFIG DEVICE and cannot be overwritten or changed by the Serial EEPROM.

- Vendor ID (0x0456)

- Product ID (0x2192)

- Device Release Number (0x0100)

- Device Attributes (0x80FA): SP (1 = self-powered, 0 = bus-powered, default = 0); RW (1 = have remote wake-up capability, 0 = no remote wake-up capability, default = 0); C[7:0] (power consumption from bus expressed in 2 mA units; default = 0xFA 500 mA)

- Manufacturer (ADI)

- Product (ADI Device)

#### **Internal Interfaces**

The ADSP-2192M provides three types of internal interfaces: registers, codec, and DSP memory buses. The following sections discuss those interfaces.

#### Register Interface

The register interface allows the PCI interface, USB interface, and both DSPs to communicate with the I/O Registers. These registers map into DSP, PCI, and USB I/O spaces.

#### **Register Spaces**

Several different register spaces are defined on the ADSP-2192M, as described in the following sections.

#### **PCI Configuration Space**

These registers control the configuration of the PCI Interface. Most of these registers are only accessible via the PCI Bus although a subset is accessible to the DSP for configuration during the boot.

#### DSP Core Register Space

Each DSP has an internal register that is accessible with no latency. These registers are accessible only from within the DSP, using the REG() instruction.

#### Peripheral Device Control Register Space

This Register Space is accessible by both DSPs, the PCI, Sub-ISA, and USB Buses. Note that certain sections of this space are exclusive to either the PCI, USB, or Sub-ISA Buses. These registers control the operation of the peripherals of the ADSP-2192M. The DSP accesses these registers using the I/O space instruction.

#### **USB Register Space**

These registers control the operation and configuration of the USB Interface. Most of these registers are only accessible via the USB Bus, although a subset is accessible to the DSP.

#### CardBus Interface

The ADSP-2192M's PC CardBus interface meets the state and timing specifications defined for PCMCIA's PC CardBus Standard April 1998 Release 6.1. It supports up to three card functions. Multiple function PC cards require a separate set of Configuration registers per function. A primary Card Information Structure common to all functions is required. Separate secondary Card Information Structures, one per function, are also required. Data for each CIS is loaded by the DSP during bootstrap loading.

The host PC can read the CIS data at any time. If needed, the WAIT control can be activated to extend the read operation to meet bus write access to the CIS data.

#### Using the PCI Interface

The ADSP-2192M includes a 33 MHz, 32-bit PCI interface to provide control and data paths between the part and the host CPU. The PCI interface is compliant with the PCI Local Bus Specification Revision 2.2. The interface supports bus mastering as well as bus target interfaces. The PCI Bus Power Management Interface Specification Revision 1.1 is supported and additional features as needed by PCI designs are included.

#### Target|Slave Interface

The ADSP-2192M PCI interface contains three separate functions, each with its own configuration space. Each function contains four base address registers used to access ADSP-2192M control registers and DSP memory. Base Address Register (BAR) 1 is used to point to the control registers. The addresses specified in these tables are offsets from BAR1 in each of the functions. PCI memory-type accesses are used to read and write the registers.

DSP memory accesses use BAR2 or BAR3 of each function. BAR2 is used to access 24-bit DSP memory; BAR3 accesses 16-bit DSP memory. Maps of the BAR2 and BAR3 registers appear in Table 8 on Page 11 and Table 9 on Page 12.

The lower half of the allocated space pointed to by each DSP memory BAR is the DSP memory for DSP core P0. The upper half is the memory space associated with DSP core P1. PCI transactions to and from DSP memory use the DMA function within the DSP core. Thus each word transferred to or from PCI

space uses a single DSP clock cycle to perform the internal DSP data transfer. Byte-wide accesses to DSP memory are not supported.

I/O type accesses are supported via BAR4. Both the control registers accessible via BAR1 and the DSP memory accessible via BAR2 and BAR3 can be accessed with I/O accesses. Indirect access is used to read and write both the control registers and the DSP memory. For the control register accesses, an address register points to the word to be accessed while a separate register is used to transfer the data. Read/write control is part of the address register. Only 16-bit accesses are possible via the I/O space.

A separate set of registers is used to perform the same function for DSP memory access. Control for these accesses includes a 24-bit/16-bit select as well as direction control. The data register for DSP memory accesses is a full 24 bits wide. 16-bit accesses will be loaded into the lower 16 bits of the register. Table 10 on Page 14 lists the registers directly accessible from BAR4.

#### **Bus Master Interface**

As a bus master, the PCI interface can transfer DMA data between system memory and the DSP. The control registers for these transfers are available both to the host and to the DSPs. Four channels of bus mastering DMA are supported on the ADSP-2192M.

Two channels are associated with the receive data and two are associated with the transmit data. The internal DSPs will typically control initiation of bus master transactions. DMA host bus master transfers can specify either standard circular buffers in system memory or perform scatter-gather DMA to host memory.

Each bus master DMA channel includes four registers to specify a standard circular buffer in system memory. The Base Address points to the start of the circular buffer. The Current Address is a pointer to the current position within that buffer. The Base Count specifies the size of the buffer in bytes, while the Current Count keeps track of how many bytes need to be transferred before the end of the buffer is reached. When the end of the buffer is reached, the channel can be programmed to loop back to the beginning and continue the transfers. When this looping occurs, a Status bit will be set in the DMA Control Register.

The PCI DMA controller can be programmed to perform scatter-gather DMA, when transferring samples to and from DSP memory. This mode allows the data to be split up in memory, and yet be transferable to and from the ADSP-2192M without processor intervention. In scatter-gather mode, the DMA controller can read the memory address and word count from an array of buffer descriptors called the Scatter-Gather Descriptor (SGD) table. This allows the DMA engine to sustain DMA transfers until all buffers in the SGD table are transferred.

To initiate a scatter-gather transfer between memory and the ADSP-2192M, the following steps are involved:

- 1. Software driver prepares a SGD table in system memory. Each descriptor is eight bytes long and consists of an address pointer to the starting address and the transfer count of the memory buffer to be transferred. In any given SGD table, two consecutive SGDs are offset by eight bytes and are aligned on a 4-byte boundary. Each SGD contains:

- a. Memory Address (Buffer Start) 4 bytes

- b. Byte Count (Buffer Size) 3 bytes

- c. End of Linked List (EOL) 1 bit (MSBit)

- d.Flag 1 bit (MSBit 1)

- 2. Initialize DMA control registers with transfer-specific information such as number of total bytes to transfer, direction of transfer, etc.

- 3. Software driver initializes the hardware pointer to the SGD table.

- 4. Engage scatter-gather DMA by writing the start value to the PCI channel Control/Status register.

- 5. The ADSP-2192M will then pull in samples as pointed to by the descriptors as needed by the DMA engine. When the EOL is reached, a status bit will be set and the DMA will end if the data buffer is not to be looped. If looping is to occur, DMA transfers will continue from the beginning of the table until the channel is turned off.

- 6. Bits in the PCI Control/Status register control whether an interrupt occurs when the EOL is reached or when the FLAG bit is set.

Scatter-gather DMA uses four registers. In scatter-gather mode the functions of the registers are mapped as shown in Table 4.

Table 4. Register Mapping in Scatter-Gather Mode

| Standard Circular<br>Buffer Mode | Scatter-Gather Mode<br>Function |

|----------------------------------|---------------------------------|

| Base Address                     | SGD Table Pointer               |

| Current Address                  | SGD Current Pointer             |

|                                  | Address                         |

| Base Count                       | SGD Pointer                     |

| Current Count                    | Current SGD Count               |

In either mode of operation, interrupts can be generated based upon the total number of bytes transferred. Each channel has two 24-bit registers to count the bytes transferred and generate interrupts as appropriate. The Interrupt Base Count register specifies the number of bytes to transfer prior to generating an interrupt. The Interrupt Count register specifies the current number left prior to generating the interrupt. When the Interrupt Count

–8– REV. 0

register reaches zero, a PCI interrupt can be generated. Also, the Interrupt Count register will be reloaded from the Interrupt Base Count and continue counting down for the next interrupt.

Table 5. PCI Interrupt Register

| Bit | Name             | Comments                   |

|-----|------------------|----------------------------|

| 0   | Reserved         | Reserve                    |

| 1   | Rx0 DMA Channel  | Receive Channel 0 Bus      |

|     | Interrupt        | Master Transactions        |

| 2   | Rx1 DMA Channel  | Receive Channel 1 Bus      |

|     | Interrupt        | Master Transactions        |

| 3   | Tx0DMAChannel    | Transmit Channel 0 Bus     |

|     | Interrupt        | Master Transactions        |

| 4   | Tx1 DMA Channel  | Transmit Channel 1 Bus     |

|     | Interrupt        | Master Transactions        |

| 5   | Incoming Mailbox | PCI to DSP Mailbox 0       |

|     | 0 PCI Interrupt  | Transfer                   |

| 6   | Incoming Mailbox | PCI to DSP Mailbox 1       |

|     | 1 PCI Interrupt  | Transfer                   |

| 7   | Outgoing Mailbox | DSP to PCI Mailbox 0       |

|     | 0 PCI Interrupt  | Transfer                   |

| 8   | Outgoing Mailbox | DSP to PCI Mailbox 1       |

|     | 1 PCI Interrupt  | Transfer                   |

| 9   | Reserved         |                            |

| 10  | Reserved         |                            |

| 11  | I/O Wake-up      | I/O Pin Initiated          |

| 12  | AC'97 Wake-up    | AC'97 Interface Initiated  |

| 13  | PCI Master Abort | PCI Interface Master Abort |

|     | Interrupt        | Detected                   |

| 14  | PCI Target Abort | PCI Interface Target Abort |

|     | Interrupt        | Detected                   |

| 15  | Reserved         |                            |

#### PCI Interrupts

There are a variety of potential sources of interrupts to the PCI host besides the bus master DMA interrupts. A single interrupt pin,  $\overline{\text{INTA}}$  is used to signal these interrupts back to the host. The PCI Interrupt Register consolidates all of the possible interrupt sources; the bits of this register are shown in Table 5. The register bits are set by the various sources, and can be cleared by writing a 1 to the bit(s) to be cleared.

#### PCI Control Register.

This register must be initialized by the DSP ROM code prior to PCI enumeration. (It has no effect in ISA or USB mode.) Once the Configuration Ready bit has been set to 1, the PCI Control Register becomes read-only, and further access by the DSP to configuration space is disallowed. The bits of this register are shown in Table 6.

#### **PCI Configuration Space**

The ADSP-2192M PCI Interface provides three separate configuration spaces, one for each possible function. This document describes the registers in each function, their reset condition, and how the three functions interact to access and control the ADSP-2192M hardware.

Table 6. PCI Control Register

| Bit  | Name                        | Comments                                                                                                                                                                          |

|------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-0  | PCI Functions<br>Configured | 00 = One PCI function<br>enabled, 01 = Two functions,<br>10 = Three functions                                                                                                     |

| 2    | Configuration<br>Ready      | When 0, disables PCI accesses to the ADSP-2192M (terminated with Retry). Must be set to 1 by DSP ROM code after initializing configuration space. Once 1, cannot be written to 0. |

| 15–3 | Reserved                    |                                                                                                                                                                                   |

#### Similarities Between the Three PCI Functions

Each function contains a complete set of registers in the predefined header region as defined in the PCI Local Bus Specification Revision 2.2. In addition, each function contains the optional registers to support PCI Bus Power Management. Generally, registers that are unimplemented or read-only in one function are similarly defined in the other functions. Each function contains four base address registers that are used to access ADSP-2192M control registers and DSP memory.

Base address register (BAR) 1 is used to access the ADSP-2192M control registers. Accesses to the control registers via BAR1 uses PCI memory accesses. BAR1 requests a memory allocation of 1024 bytes. Access to DSP memory occurs via BAR2 and BAR3. BAR2 is used to access 24-bit DSP memory (for DSP program downloading) while BAR3 is used to access 16-bit DSP memory. BAR4 provides I/O space access to both the control registers and the DSP memory.

Table 7 shows the configuration space headers for the three spaces. While these are the default uses for each of the configurations, they can be redefined to support any possible function by writing to the class code register of that function during boot. Additionally, during boot time, the DSP can disable one or more of the functions. If only two functions are enabled, they will be functions 0 and 1. If only one function is enabled, it will be function 0.

#### Interactions Between the Three PCI Configurations

Because the configurations must access and control a single set of resources, potential conflicts can occur between the control specified by the configuration.

Target accesses to registers and DSP memory can go through any function. As long as the Memory Space access enable bit is set in that function, then PCI memory accesses whose addresses match the locations programmed into a function, BARs 1–3 will be able to read or write any visible register or memory location within the ADSP-2192M. Similarly, if I/O space access enable is set, then PCI I/O accesses can be performed via BAR4.

Within the Power Management section of the configuration blocks, there are a few interactions. The part will stay in the highest power state between the three configurations.

REV. 0 –9–

Table 7. PCI Configuration Space 0, 1, and 2

| Address     | Name                            | Reset   | Comments                                        |

|-------------|---------------------------------|---------|-------------------------------------------------|

| 0x01-0x00   | Vendor ID                       | 0x11D4  | Writable from the DSP during initialization     |

| 0x03-0x02   | Config 0 Device ID              | 0x2192  | Writable from the DSP during initialization     |

|             | Config 1 Device ID              | 0x219A  | Writable from the DSP during initialization     |

|             | Config 2 Device ID              | 0x219E  | Writable from the DSP during initialization     |

| 0x05-0x04   | Command Register                | 0x0     | Bus Master, Memory Space Capable, I/O Space     |

|             |                                 |         | Capable                                         |

| 0x07-0x06   | Status Register                 | 0x0     | Bits enabled: Capabilities List, Fast B2B,      |

|             |                                 |         | Medium Decode                                   |

| 0x08        | Revision ID                     | 0x0     | Writable from the DSP during initialization     |

| 0x0B-0x09   | Class Code                      | 0x48000 | Writable from the DSP during initialization     |

| 0x0C        | Cache Line Size                 | 0x0     | Read Only                                       |

| 0x0D        | Latency Timer                   | 0x0     |                                                 |

| 0x0E        | Header Type                     | 0x80    | Multifunction bit set                           |

| 0x0F        | BIST                            | 0x0     | Unimplemented                                   |

| 0x13-0x10   | Base Address 1                  | 0x08    | Register Access for all ADSP-2192M Registers,   |

|             |                                 |         | Prefetchable Memory                             |

| 0x17 - 0x14 | Base Address2                   | 0x08    | 24-bit DSP Memory Access                        |

| 0x1B-0x18   | Base Address3                   | 0x08    | 16-bit DSP Memory Access                        |

| 0x1F-0x1C   | Base Address4                   | 0x01    | I/O access for control registers and DSP memory |

| 0x23-0x20   | Base Address5                   | 0x0     | Unimplemented                                   |

| 0x27 - 0x24 | Base Address6                   | 0x0     | Unimplemented                                   |

| 0x2B-0x28   | Config 0 CardBus CIS Pointer    | 0x1FF03 | CIS RAM Pointer - Function 0 (Read Only)        |

|             | Config 1 CardBus CIS Pointer    | 0x1FE03 | CIS RAM Pointer - Function 1 (Read Only)        |

|             | Config 2 CardBus CIS Pointer    | 0x1FD03 | CIS RAM Pointer - Function 2 (Read Only)        |

| 0x2D-0x2C   | Subsystem Vendor ID             | 0x11D4  | Writable from the DSP during initialization     |

| 0x2F-0x2E   | Config 0 Subsystem Device ID    | 0x2192  | Writable from the DSP during initialization     |

|             | Config 1 Subsystem Device ID    | 0x219A  | Writable from the DSP during initialization     |

|             | Config 2 Subsystem Device ID    | 0x219E  | Writable from the DSP during initialization     |

| 0x33-0x30   | Expansion ROM Base Address      | 0x0     | Unimplemented                                   |

| 0x34        | Capabilities Pointer            | 0x40    | Read Only                                       |

| 0x3C        | Interrupt Line                  | 0x0     |                                                 |

| 0x3D        | Interrupt Pin                   | 0x1     | Uses INTA Pin                                   |

| 0x3E        | Min_Gnt                         | 0x1     | Read Only                                       |

| 0x3F        | Max_Lat                         | 0x4     | Read Only                                       |

| 0x40        | Capability ID                   | 0x1     | Power Management Capability Identifier          |

| 0x41        | Next_Cap_Ptr                    | 0x0     | Read Only                                       |

| 0x43 - 0x42 | Power Management Capabilities   | 0x6C22  | Writable from the DSP during initialization     |

| 0x45 - 0x44 | Power Management Control/Status | 0x0     | Bits 15 and 8 initialized only on Power-up      |

| 0x46        | Power Management Bridge         | 0x0     | Unimplemented                                   |

| 0x47        | Power Management Data           | 0x0     | Unimplemented                                   |

#### PCI Memory Map

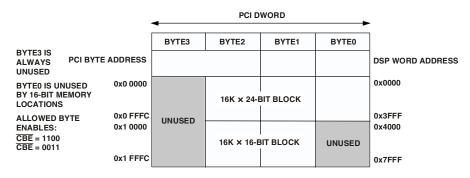

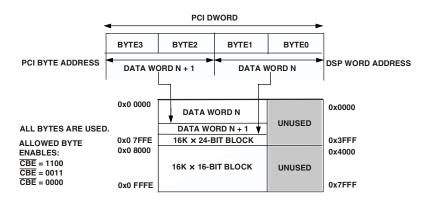

The ADSP-2192M On-Chip Memory is mapped to the PCI Address Space. Because some ADSP-2192M Memory Blocks are 24 bits wide (Program Memory) while others are 16 bits (Data Memory), two different footprints are available in PCI Address Space. These footprints are available to each PCI function by accessing different PCI Base Address Registers (BAR). BAR2 supports 24-bit "Unpacked" Memory Access. BAR3 supports 16-bit "Packed" Memory Access.

In 24-bit (BAR2) Mode, each 32 bits (four Consecutive PCI Byte Address Locations, which make up one PCI Data word) correspond to a single ADSP-2192M Memory Location. BAR2

Mode is typically used for Program Memory Access. Byte3 is always unused. Bytes[2:0] are used for 24-bit Memory Locations. As shown in Figure 3, Bytes[2:1] are used for 16-bit Memory Locations.

In 16-bit (BAR3) Mode (Figure 4), each 32-bit (four Consecutive PCI Byte Address Locations) PCI Data Word corresponds to two ADSP-2192M Memory Locations. Bytes[3:2] contain one 16-bit Data Word, Bytes[1:0] contain a second 16-bit Data Word. BAR3 Mode is typically used for Data Memory Access. Only the 16 MSBs of a Data Word are accessed in 24-bit Blocks; the 8 LSBs are ignored.

-10- REV. 0

Figure 3. PCI Addressing for 24-Bit and 16-Bit Memory Blocks in 24-Bit Access (BAR2) Mode

Figure 4. PCI Addressing for 24-Bit and 16-Bit Memory Blocks in 16-Bit Access (BAR3) Mode

#### 24-Bit PCI DSP Memory Map (BAR2)

The complete PCI address footprint for the ADSP-2192M DSP Memory Spaces in 24-bit (BAR2) Mode is shown in Table 8.

Table 8. 24-Bit PCI DSP Memory Map (BAR2 Mode)<sup>1</sup>

| Block              | Byte3      | Byte2    | Byte1   | Byte0      | Offset      |

|--------------------|------------|----------|---------|------------|-------------|

| DSP P0 Data RAM    | UNUSED     | D[15:8]  | D[7:0]  | UNUSED     | 0x0000 0000 |

| Block 0            | UNUSED     | D[15:8]  | D[7:0]  | UNUSED     | 0x0000 0004 |

|                    | <br>UNUSED | D[15:8]  | D[7:0]  | <br>UNUSED | 0x0000 FFFC |

| DSP P0 Data RAM    | UNUSED     | D[15:8]  | D[7:0]  | UNUSED     | 0x0001 0000 |

| Block 1            | UNUSED     | D[15:8]  | D[7:0]  | UNUSED     | 0x0001 0004 |

|                    | <br>UNUSED | D[15:8]  | D[7:0]  | <br>UNUSED | 0x0001 FFFC |

| DSP P0 Data RAM    | UNUSED     | D[15:8]  | D[7:0]  | UNUSED     | 0x0002 0000 |

| Block 2            | UNUSED     | D[15:8]  | D[7:0]  | UNUSED     | 0x0002 0004 |

|                    | <br>UNUSED | D[15:8]  | D[7:0]  | UNUSED     | 0x0002 FFFC |

| DSP P0 Data RAM    | UNUSED     | D[15:8]  | D[7:0]  | UNUSED     | 0x0003 0000 |

| Block 3            | UNUSED     | D[15:8]  | D[7:0]  | UNUSED     | 0x0003 0004 |

| _                  | <br>UNUSED | D[15:8]  | D[7:0]  | <br>UNUSED | 0x0003 FFFC |

| DSP P0 Program RAM | UNUSED     | D[23:16] | D[15:8] | D[7:0]     | 0x0004 0000 |

| Block              | UNUSED     | D[23:16] | D[15:8] | D[7:0]     | 0x0004 0004 |

|                    | <br>UNUSED | D[23:16] | D[15:8] | D[7:0]     | 0x0004 FFFC |

REV. 0 –11–

Table 8. 24-Bit PCI DSP Memory Map (BAR2 Mode)<sup>1</sup> (continued)

| Block              | Byte3    | Byte2    | Byte1    | Byte0    | Offset      |

|--------------------|----------|----------|----------|----------|-------------|

| DSP P0 Program ROM | UNUSED   | D[23:16] | D[15:8]  | D[7:0]   | 0x0005 0000 |

| Block              | UNUSED   | D[23:16] | D[15:8]  | D[7:0]   | 0x0005 0004 |

|                    | UNUSED   | D[23:16] | D[15:8]  | D[7:0]   | 0x0005 3FFC |

| Reserved Space     | RESERVED | RESERVED | RESERVED | RESERVED | 0x0005 4000 |

|                    | RESERVED | RESERVED | RESERVED | RESERVED | 0x0007 FFFC |

| DSP P1 Data RAM    | UNUSED   | D[15:8]  | D[7:0]   | UNUSED   | 0x0008 0000 |

| Block 0            | UNUSED   | D[15:8]  | D[7:0]   | UNUSED   | 0x0008 0004 |

|                    | UNUSED   | D[15:8]  | D[7:0]   | UNUSED   | 0x0008 FFFC |

| DSP P1 Data RAM    | UNUSED   | D[15:8]  | D[7:0]   | UNUSED   | 0x0009 0000 |

| Block 1            | UNUSED   | D[15:8]  | D[7:0]   | UNUSED   | 0x0009 0004 |

|                    | UNUSED   | D[15:8]  | D[7:0]   | UNUSED   | 0x0009 FFFC |

| Reserved Space     | UNUSED   | D[15:8]  | D[7:0]   | UNUSED   | 0x000A 0000 |

|                    | UNUSED   | D[15:8]  | D[7:0]   | UNUSED   | 0x000A 0004 |

|                    | UNUSED   | D[15:8]  | D[7:0]   | UNUSED   | 0x000B FFFC |

| DSP P1 Program RAM | UNUSED   | D[23:16] | D[15:8]  | D[7:0]   | 0x000C 0000 |

| Block              | UNUSED   | D[23:16] | D[15:8]  | D[7:0]   | 0x000C 0004 |

|                    | UNUSED   | D[23:16] | D[15:8]  | D[7:0]   | 0x000C FFFC |

| DSP P1 Program ROM | UNUSED   | D[23:16] | D[15:8]  | D[7:0]   | 0x000D 0000 |

| Block              | UNUSED   | D[23:16] | D[15:8]  | D[7:0]   | 0x000D 0004 |

|                    | UNUSED   | D[23:16] | D[15:8]  | D[7:0]   | 0x000D 3FFC |

| Reserved Space     | RESERVED | RESERVED | RESERVED | RESERVED | 0x000D 4000 |

|                    | RESERVED | RESERVED | RESERVED | RESERVED | 0x000F FFFC |

$<sup>^{1}\</sup>mathrm{The}$  ". . . " entries in this table indicate the continuation of the pattern shown in the first rows of each section.

### 16-Bit PCI DSP Memory Map (BAR3)

The complete PCI address footprint for the ADSP-2192M DSP Memory Spaces in 16-bit (BAR3) Mode is shown in Table 9.

Table 9. 16-Bit PCI DSP Memory Map (BAR3 Mode)<sup>1</sup>

| Block                      | Byte3              | Byte2            | Byte1              | Byte0            | Offset                     |

|----------------------------|--------------------|------------------|--------------------|------------------|----------------------------|

| DSP P0 Data RAM<br>Block 0 | D[15:8]<br>D[15:8] | D[7:0]<br>D[7:0] | D[15:8]<br>D[15:8] | D[7:0]<br>D[7:0] | 0x0000 0000<br>0x0000 0004 |

| Dio Cir o                  | D[15:8]            | D[7:0]           | D[15:8]            | D[7:0]           | 0x0000 7FFC                |

| DSP P0 Data RAM<br>Block 1 | D[15:8]<br>D[15:8] | D[7:0]<br>D[7:0] | D[15:8]<br>D[15:8] | D[7:0]<br>D[7:0] | 0x0000 8000<br>0x0000 8004 |

|                            | D[15:8]            | D[7:0]           | D[15:8]            | D[7:0]           | 0x0000 FFFC                |

| DSP P0 Data RAM<br>Block 2 | D[15:8]<br>D[15:8] | D[7:0]<br>D[7:0] | D[15:8]<br>D[15:8] | D[7:0]<br>D[7:0] | 0x0001 0000<br>0x0001 0004 |

|                            | D[15:8]            | D[7:0]           | D[15:8]            | D[7:0]           | 0x0001 7FFC                |

-12- REV. 0

Table 9. 16-Bit PCI DSP Memory Map (BAR3 Mode)<sup>1</sup> (continued)

| Block                       | Byte3                | Byte2              | Byte1                | Byte0              | Offset                     |

|-----------------------------|----------------------|--------------------|----------------------|--------------------|----------------------------|

| DSP P0 Data RAM<br>Block 3  | D[15:8]<br>D[15:8]   | D[7:0]<br>D[7:0]   | D[15:8]<br>D[15:8]   | D[7:0]<br>D[7:0]   | 0x0001 8000<br>0x0001 8004 |

|                             | D[15:8]              | D[7:0]             | D[15:8]              | D[7:0]             | 0x0001 FFFC                |

| DSP P0 Program RAM<br>Block | D[23:16]<br>D[23:16] | D[15:8]<br>D[15:8] | D[23:16]<br>D[23:16] | D[15:8]<br>D[15:8] | 0x0002 0000<br>0x0002 0004 |

|                             | D[23:16]             | D[15:8]            | D[23:16]             | D[15:8]            | 0x0002 7FFC                |

| DSP P0 Program ROM<br>Block | D[23:16]<br>D[23:16] | D[15:8]<br>D[15:8] | D[23:16]<br>D[23:16] | D[15:8]<br>D[15:8] | 0x0002 8000<br>0x0002 8004 |

|                             | D[23:16]             | D[15:8]            | D[23:16]             | D[15:8]            | 0x0002 9FFC                |

| Reserved Space              | RESERVED             | RESERVED           | RESERVED             | RESERVED           | 0x0002 A000                |

|                             | RESERVED             | RESERVED           | RESERVED             | RESERVED           | 0x0003 FFFC                |

| DSP P1 Data RAM<br>Block 0  | D[15:8]<br>D[15:8]   | D[7:0]<br>D[7:0]   | D[15:8]<br>D[15:8]   | D[7:0]<br>D[7:0]   | 0x0004 0000<br>0x0004 0004 |

|                             | D[15:8]              | D[7:0]             | D[15:8]              | D[7:0]             | 0x0004 7FFC                |

| DSP P1 Data RAM<br>Block 1  | D[15:8]<br>D[15:8]   | D[7:0]<br>D[7:0]   | D[15:8]<br>D[15:8]   | D[7:0]<br>D[7:0]   | 0x0004 8000<br>0x0004 8004 |

|                             | D[15:8]              | D[7:0]             | D[15:8]              | D[7:0]             | 0x0004 FFFC                |

| Reserved Space              | RESERVED             | RESERVED           | RESERVED             | RESERVED           | 0x0005 0000                |

|                             | RESERVED             | RESERVED           | RESERVED             | RESERVED           | 0x0005 FFFC                |

| DSP P1 Program RAM<br>Block | D[23:16]<br>D[23:16] | D[15:8]<br>D[15:8] | D[23:16]<br>D[23:16] | D[15:8]<br>D[15:8] | 0x0006 0000<br>0x0006 0004 |

|                             | D[23:16]             | D[15:8]            | D[23:16]             | D[15:8]            | 0x0006 7FFC                |

| DSP P1 Program ROM<br>Block | D[23:16]<br>D[23:16] | D[15:8]<br>D[15:8] | D[23:16]<br>D[23:16] | D[15:8]<br>D[15:8] | 0x0006 8000<br>0x0006 8004 |

|                             | D[23:16]             | D[15:8]            | D[23:16]             | D[15:8]            | 0x0006 9FFC                |

| Reserved Space              | RESERVED             | RESERVED           | RESERVED             | RESERVED           | 0x0006 A000                |

| _                           | RESERVED             | RESERVED           | RESERVED             | RESERVED           | 0x0007 FFFC                |

$<sup>^1\</sup>mathrm{The}$  ". . ." entries in this table indicate the continuation of the pattern shown in the first rows of each section.

#### 16-Bit PCI DSP I/O Memory Map (BAR4)

PCI Base Address Register (BAR4) allows indirect access to the ADSP-2192M Control Registers and DSP Memory. The DSP Memory Indirect Access Registers accessible from BAR4 are shown in Table 10.

DSP P0 Memory Indirect Address Space occupies PCI BAR4 Space 0x000000 through 0x01FFFF

DSP P1 Memory Indirect Address Space occupies PCI BAR4 Space 0x020000 through 0x03FFFF

All Indirect DSP Memory Accesses are 24-bit or 16-bit Word Accesses.

#### Using the USB Interface

The ADSP-2192M USB design enables the ADSP-2192M to be configured and attached to a single device with multiple interfaces and various endpoint configurations, as follows:

- Programmable descriptors and a class-specific command interpreter are accessible through the USB 8052 registers. An 8052 compatible MCU is supported on-board, to enable soft downloading of different configurations, and support of standard or class-specific commands.

- A total of eight user-defined endpoints are provided. Endpoints can be configured as BULK, ISO, or INT, and can be grouped.

REV. 0 –13–

Table 10. 16-Bit PCI DSP I/O Space Indirect Access Registers Map (BAR4 Mode)

| Offset      | Name                | Reset    | Comments                      |

|-------------|---------------------|----------|-------------------------------|

| 0x03-0x00   | Control             | 0x0000   | Address and direction         |

|             | Register<br>Address |          | control for register accesses |

| 0x07 - 0x04 | Control             | 0x0000   | Data for register             |

|             | Register            |          | accesses                      |

|             | Data                |          |                               |

| 0x0B-0x08   | DSP                 | 0x000000 | Address and Direction         |

|             | Memory              |          | control for Indirect          |

|             | Address             |          | DSP memory accesses           |

| 0x0F-0x0C   | DSP                 | 0x000000 | Data for DSP memory           |

|             | Memory              |          | accesses                      |

|             | Data                |          |                               |

#### **USB DSP Register Definitions**

For each endpoint, four registers are defined to provide a memory buffer in the DSP. These registers are defined for each endpoint shared by all defined interfaces, for a total of  $4 \times 8 = 32$  registers. These registers are read/write by the DSP only. They are described in Table 11.

Table 11. USB DSP Register Definitions

| Page   | Address                | Name                           | Comment |

|--------|------------------------|--------------------------------|---------|

| 0x0C   | 0x0-0x3                | DSP Memory Buffer Base         | EP4     |

|        |                        | Addr                           |         |

| 0x0C   | 0x4-0x5                | DSP Memory Buffer Size         | EP4     |

| 0x0C   | 0x6-0x7                | DSP Memory Buffer RD           | EP4     |

|        |                        | Offset                         |         |

| 0x0C   | 0x8-0x9                | DSP Memory Buffer WR           | EP4     |

|        |                        | Offset                         |         |

| 0x0C   | 0x10-0x13              | DSP Memory Buffer Base         | EP5     |

|        |                        | Addr                           |         |

| 0x0C   |                        | DSP Memory Buffer Size         | EP5     |

| 0x0C   | 0x16-0x17              | DSP Memory Buffer RD           | EP5     |

| 0.00   | 0 10 0 10              | Offset                         | ED5     |

| 0x0C   | 0x18-0x19              | DSP Memory Buffer WR<br>Offset | EP5     |

| 0x0C   | 0x20-0x23              | DSP Memory Buffer Base         | EP6     |

| UXUC   | 0x20-0x23              | Addr                           | EFO     |

| 0x0C   | 0x24-0x25              | DSP Memory Buffer Size         | EP6     |

| 0x0C   | 0x24-0x25<br>0x26-0x27 | DSP Memory Buffer RD           | EP6     |

| OXOC   | 0220 021               | Offset                         |         |

| 0x0C   | 0x28-0x29              | DSP Memory Buffer WR           | EP6     |

| 0110 0 |                        | Offset                         | 21 0    |

| 0x0C   | 0x30-0x33              | DSP Memory Buffer Base         | EP7     |

|        |                        | Addr                           |         |

| 0x0C   | 0x34-0x35              | DSP Memory Buffer Size         | EP7     |

| 0x0C   | 0x36-0x37              | DSP Memory Buffer RD           | EP7     |

|        |                        | Offset                         |         |

| 0x0C   | 0x38-0x39              | DSP Memory Buffer WR           | EP7     |

|        |                        | Offset                         |         |

| 0x0C   | 0x40-0x43              | DSP Memory Buffer Base         | EP8     |

|        |                        | Addr                           |         |

| 0x0C   | 0x44-0x45              | DSP Memory Buffer Size         | EP8     |

Table 11. USB DSP Register Definitions (continued)

| Page         | Address       | Name                                           | Comment |  |

|--------------|---------------|------------------------------------------------|---------|--|

| 0x0C         | 0x46-0x47     | DSP Memory Buffer RD                           | EP8     |  |

|              |               | Offset                                         |         |  |

| 0x0C         | 0x48-0x49     | DSP Memory Buffer WR                           | EP8     |  |

|              |               | Offset                                         |         |  |

| 0x0C         | 0x50-0x53     | DSP Memory Buffer Base                         | EP9     |  |

| 000          | 0x54-0x55     | Addr<br>DSB Marrager Buffer Sing               | EP9     |  |

| 0x0C<br>0x0C |               | DSP Memory Buffer Size                         | EP9     |  |

| UXUC         | 0x30-0x37     | DSP Memory Buffer RD<br>Offset                 | EP9     |  |

| 0x0C         | 0x58-0x59     | DSP Memory Buffer WR                           | EP9     |  |

| 0110 0       |               | Offset                                         |         |  |

| 0x0C         | 0x60-0x63     | DSP Memory Buffer Base                         | EP10    |  |

|              |               | Addr                                           |         |  |

| 0x0C         | 0x64-0x65     | DSP Memory Buffer Size                         | EP10    |  |

| 0x0C         | 0x66-0x67     | DSP Memory Buffer RD                           | EP10    |  |

|              |               | Offset                                         |         |  |

| 0x0C         | 0x68-0x69     | DSP Memory Buffer WR   EP10                    |         |  |

|              |               | Offset                                         | 777.1   |  |

| 0x0C         | 0x70-0x73     | DSP Memory Buffer Base                         | EP11    |  |

| 0x0C         | 0x74-0x75     | Addr<br>DSB Marrager Buffer Sing               | EP11    |  |

| 0x0C         |               | DSP Memory Buffer Size<br>DSP Memory Buffer RD | EP11    |  |

| UXUC         | UX / 0-UX / / | Offset                                         | EPII    |  |

| 0x0C         | 0x78-0x79     | DSP Memory Buffer WR                           | EP11    |  |

| onec         | on on on      | Offset                                         | 2111    |  |

| 0x0C         | 0x80-0x81     | USB Descriptor Vendor                          |         |  |

|              |               | ID                                             |         |  |

| 0x0C         | 0x84-0x85     | USB Descriptor Product                         |         |  |

|              |               | ID                                             |         |  |

| 0x0C         | 0x86-0x87     |                                                |         |  |

|              |               | Number                                         |         |  |

| 0x0C         | 0x88-0x89     | USB Descriptor Device                          |         |  |

|              |               | Attributes                                     |         |  |

#### USB DSP Memory Buffer Base Addr Register

Points to the base address for the DSP memory buffer assigned to this endpoint.

BA[17:0] = Memory Buffer Base Address

#### USB DSP Memory Buffer Size Register

Indicates the size of the DSP memory buffer assigned to this endpoint.

SZ[15:0] = Memory Buffer Size

#### USB DSP Memory Buffer RD Pointer Offset Register

The offset from the base address for the read pointer of the memory buffer assigned to this endpoint.

RD[15:0] = Memory Buffer RD Offset

#### USB DSP Memory Buffer WR Pointer Offset Register

The offset from the base address for the write pointer of the memory buffer assigned to this endpoint.

WR[15:0] = Memory Buffer WR Offset

-14- REV. 0

#### USB Descriptor Vendor ID

The Vendor ID returned in the GET DEVICE DESCRIPTOR command is contained in this register. The DSP can change the Vendor ID by writing to this register during the Serial EEPROM initialization. The default Vendor ID is 0x0456, which corresponds to Analog Devices, Inc.

V[15:0] = Vendor ID (default = 0x0456)

#### USB Descriptor Product ID

The Product ID returned in the GET DEVICE DESCRIPTOR command is contained in this register. The DSP can change the Product ID by writing to this register during the Serial EEPROM initialization. The default Product ID is 0x2192.

P[15:0] = Product ID (default = 0x2192)

#### USB Descriptor Release Number

The Release Number returned in the GET DEVICE DESCRIP-TOR command is contained in this register. The DSP can change the Release Number by writing to this register during the Serial EEPROM initialization. The default Release Number is 0x0100, which corresponds to Version 01.00.

R[15:0] = Release Number (default = 0x0100)

#### USB Descriptor Device Attributes

The device-specific attributes returned in the GET DEVICE DESCRIPTOR command are contained in this register. The DSP can change the attributes by writing to this register during the Serial EEPROM initialization. The default attributes are 0x80FA, which correspond to bus-powered, no remote wake-up, and max power = 500 mA.

- SP: 1 = self-powered, 0 = bus-powered (default = 0)

- RW: 1 = have remote wake-up capability, 0 = no remote wake-up capability (default = 0)

- C[7:0] = power consumption from bus, expressed in 2 mA units (default = xFA 500 mA)

#### USB DSP MCU Register Definitions

MCU registers, described in Table 12, are defined in four memory spaces that are grouped by the following address ranges:

- 0x0XXX—This address range defines general-purpose USB status and control registers

- 0x1XXX—This address range defines registers that are specific to endpoint setup and control

- 0x2XXX—This address range defines the registers used for REGIO accesses to the DSP register space

- 0x3XXX—This address range defines the MCU program memory write address space

Table 12. USB MCU Register Definitions

| Address         | Name                               | Comments                                         |

|-----------------|------------------------------------|--------------------------------------------------|

| 0x0000-0x0007   | USB SETUP Token Cmd                | Eight Bytes Total                                |

| 0x0008-0x000F   | USB SETUP Token Data               | Eight Bytes Total                                |

| 0x0010-0x0011   | USB SETUP Counter                  | 16-bit Counter                                   |

| 0x0012 - 0x0013 | USB Control                        | Miscellaneous control including re-attach        |

| 0x0014-0x0015   | USB Address/Endpoint               | Address of device/active endpoint                |

| 0x0016-0x0017   | USB Frame Number                   | Current frame number                             |

| 0x0030-0x0031   | USB Serial EEPROM Mailbox 1        | Defined by Analog Devices                        |

| 0x0032-0x0033   | USB Serial EEPROM Mailbox 2        | Defined by Analog Devices                        |

| 0x0034-0x0035   | USB Serial EEPROM Mailbox 3        | Defined by Analog Devices                        |

| 0x1000-0x1001   | USB EP4 Description                | Configures endpoint                              |

| 0x1002-0x1003   | USB EP4 NAK                        | Counter                                          |

| 0x1004-0x1005   | USB EP5 Description                | Configures endpoint                              |

| 0x1006-0x1007   | USB EP5 NAK                        | Counter                                          |

| 0x1008-0x1009   | USB EP6 Description                | Configures endpoint                              |

| 0x100A-0x100B   | USB EP6 NAK                        | Counter                                          |

| 0x100C-0x100D   | USB EP7 Description                | Configures endpoint                              |

| 0x100E-0x100F   | USB EP7 NAK                        | Counter                                          |

| 0x1010-0x1011   | USB EP8 Description                | Configures endpoint                              |

| 0x1012-0x1013   | USB EP8 NAK                        | Counter                                          |

| 0x1014-0x1015   | USB EP8 Description                | Configures endpoint                              |

| 0x1016-0x1017   | USB EP9 NAK                        | Counter                                          |

| 0x1018-0x1019   | USB EP10 Description               | Configures endpoint                              |

| 0x101A-0x101B   | USB EP10 NAK                       | Counter                                          |

| 0x101C-0x101D   | USB EP11 Description               | Configures endpoint                              |

| 0x101E-0x101F   | USB EP11 NAK                       | Counter                                          |

| 0x1020-0x1021   | USB EP STALL                       | Policy                                           |

| 0x1040-0x1043   | USB EP1 Code Download Base Address | Starting address for code download on endpoint 1 |

REV. 0 –15–

Table 12. USB MCU Register Definitions (continued)

| Address       | Name                                      | Comments                                                     |

|---------------|-------------------------------------------|--------------------------------------------------------------|

| 0x1044-0x1047 | USB EP2 Code Download Base Address        | Starting address for code download on endpoint 2             |

| 0x1048-0x104B | USB EP3 Code Download Base Address        | Starting address for code download on endpoint 3             |

| 0x1060-0x1063 | USB EP1 Code Current Write Pointer Offset | Current write pointer offset for code download on endpoint 1 |

| 0x1064-0x1067 | USB EP2 Code Current Write Pointer Offset | Current write pointer offset for code download on endpoint 2 |

| 0x1068-0x106B | USB EP3 Code Current Write Pointer Offset | Current write pointer offset for code download on endpoint 3 |

| 0x2000-0x2001 | USB Register I/O Address                  |                                                              |

| 0x2002-0x2003 | USB Register I/O Data                     |                                                              |

| 0x3000-0x3FFF | USB MCU Program Memory                    |                                                              |

#### USB Endpoint Description Register

The endpoint description register provides the USB core with information about the endpoint type, direction, and max packet size. This register is read/write by the MCU only. This register is defined for endpoints 4–11.

- PS[9:0] MAX Packet Size for endpoint

- LT[1:0] Last transaction indicator bits: 00 = Clear, 01 = ACK, 10 = NAK, or 11 = ERR

- TY[1:0] Endpoint type bits: 00 = DISABLED, 01 = ISO, 10 = Bulk, or 11 = Interrupt

- DR Endpoint direction bit: 1 = IN or 0 = OUT

- TB Toggle bit for endpoint. Reflects the current state of the DATA toggle bit.

#### USB Endpoint NAK Counter Register

This register records the number of sequential NAKs that have occurred on a given endpoint. This register is defined for endpoints 4–11. This register is read/write by the MCU only.

- N[3:0] NAK counter. Number of sequential NAKs that have occurred on a given endpoint. When N[3:0] is equal to the base NAK counter NK[3:0], a zero-length packet or packet less that maxpacketsize will be issued.

- ST 1 = Endpoint is stalled

#### USB Endpoint Stall Policy Register

This register contains NAK count and endpoint FIFO error policy bit. The STALL status bits for endpoints 1–3 are included as well. This register is read/write by the MCU only.

- ST[3:1] 1 = Endpoint is stalled. ST[1] maps to endpoint 1, ST[2] maps to endpoint 2, etc.

- NK[3:0] Base NAK counter. Determines how many sequential NAKs are issued before sending zero length packet on any given endpoint.

- FE FIFO error policy. 1 = When endpoint FIFO is overrun/underrun, STALL endpoint

#### USB Endpoint 1 Code Download Base Address Register

This register contains an 18-bit address which corresponds to the starting location for DSP code download on endpoint 1. This register is read/write by the MCU only.

#### USB Endpoint 2 Code Download Base Address Register

This register contains an 18-bit address which corresponds to the starting location for DSP code download on endpoint 2. This register is read/write by the MCU only.

#### USB Endpoint 3 Code Download Base Address Register

This register contains an 18-bit address which corresponds to the starting location for DSP code download on endpoint 3. This register is read/write by the MCU only.

#### USB Endpoint 1 Code Current Write Pointer Offset Register

This register contains an 18-bit address which corresponds to the current write pointer offset from the base address register for DSP code download on endpoint 1. The sum of this register and the EP1 Code Download Base Address Register represents the last DSP PM location written.

This register is read by the MCU only and is cleared to 3FFFF (-1) when the Endpoint 1 Code Download Base Address Register is updated.

#### USB Endpoint 2 Code Current Write Pointer Offset Register

This register contains an 18-bit address that corresponds to the current write pointer offset from the base address register for DSP code download on endpoint 2. The sum of this register and the EP2 Code Download Base Address Register represents the last DSP PM location written.

This register is read by the MCU only and is cleared to 3FFFF (-1) when the Endpoint 2 Code Download Base Address Register is updated.

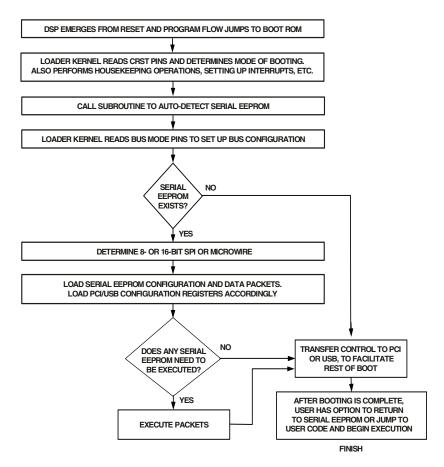

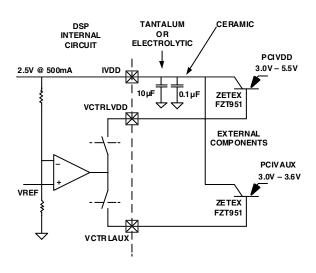

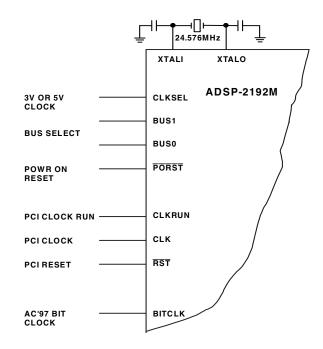

#### USB Endpoint 3 Code Current Write Pointer Offset Register